- 您现在的位置:买卖IC网 > Sheet目录1223 > KSZ9692PB-EVAL (Micrel Inc)BOARD EVALUATION FOR KSZ9692PB

�� �

�

�

�Micrel,� Inc.�

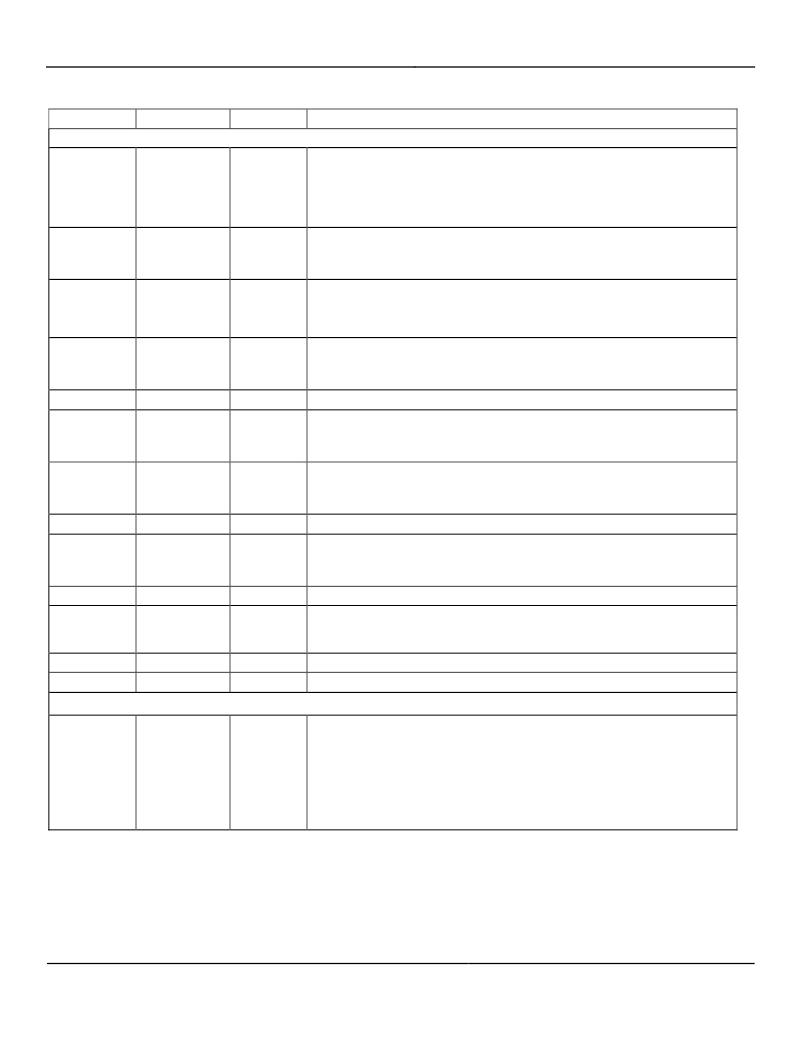

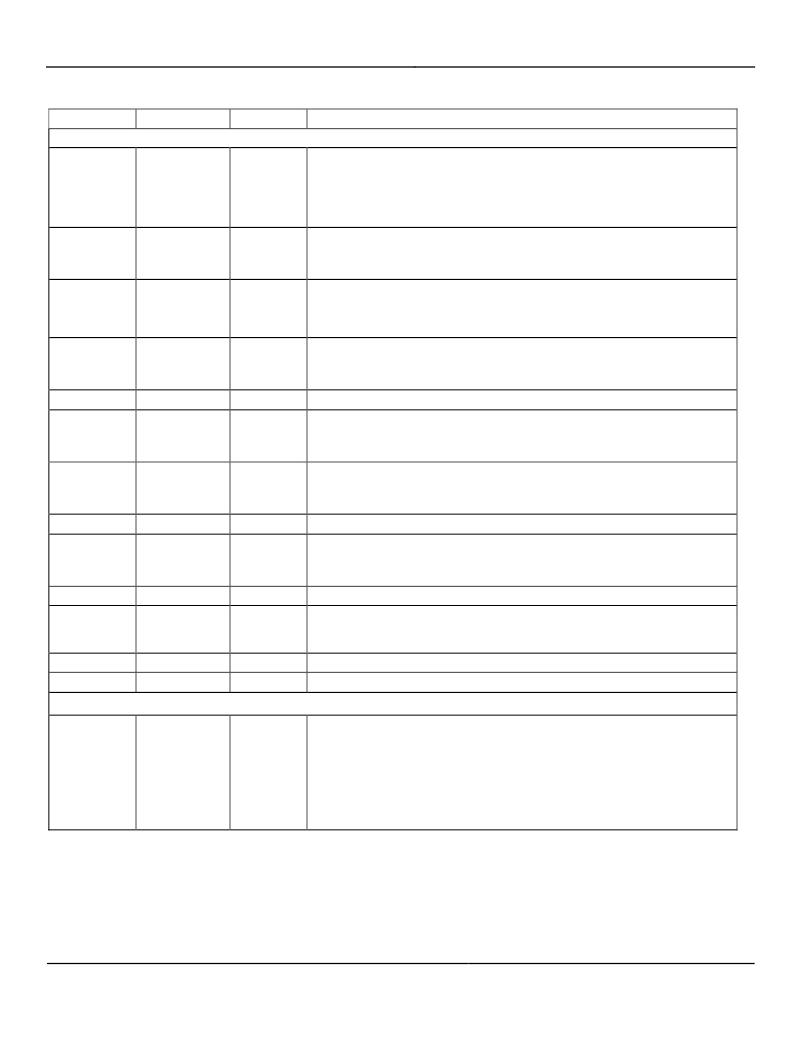

�Pin� Description:� Signal� Descriptions� by� Group�

�KSZ9692PB,� KSZ9692PB-S�

�Pin� Number�

�Pin� Name�

�Pin� Type�

�Pin� Description�

�System� Interface�

�R5�

�RESETN�

�I�

�Reset,� asserted� Low.�

�RESETN� will� force� the� KSZ9692PB,� KSZ9692PB-S� to� reset� ARM9� CPU� and� all�

�functional� blocks.� Once� asserted,� RESETN� must� remain� asserted� for� a�

�minimum� duration� of� 256� system� clock� cycles.� When� in� the� reset� state,� all� the�

�output� pins� are� put� into� Tri-state� and� all� open� drain� signals� are� floated.�

�N5�

�WRSTO�

�O�

�Watchdog� Timer� Reset� Output�

�When� the� Watchdog� Timer� expires,� this� signal� will� be� asserted� for� at� least� 200�

�msec.�

�W1�

�XCLK2�

�I�

�System� Clock� Input� 2.�

�External� crystal� or� clock� input� 2.� The� clock� frequency� should� be�

�25MHz� ±� 50ppm.�

�Y1�

�XCLK1�

�I�

�System� Clock� Input� 1.�

�Used� with� XCLK1� pin� when� other� polarity� of� crystal� is� needed.� This� is� unused�

�for� a� normal� clock� input.�

�H19�

�Y15,� Y14�

�CLK25MHz�

�DDCLKO[1:0]�

�O�

�O�

�25MHz� output� to� external� PHY�

�DDR� Clock� Out� [1:0].�

�Output� of� the� internal� system� clock,� it� is� also� used� as� the� clock� signal� for� DDR�

�interface.�

�W15,� W14�

�DDCLKON[1:0]�

�O�

�The� negative� of� differential� pair� of� DDR� Clock� Out� [1:0].�

�Output� of� the� internal� system� clock,� it� is� also� used� as� the� clock� signal� for� DDR�

�interface.�

�U13�

�T7,� U7�

�SDCLKEO�

�VREF�

�O�

�I�

�Clock� Enable� output� for� SDRAM� (for� Power� Down� Mode)�

�Reference� Voltage� for� SSTL� interface.�

�Must� be� half� of� the� voltage� for� the� DDR� VDD� supply.� See� EIA/JEDEC� standard�

�EIA/JESD8-9� (Stub� series� terminated� logic� for� 2.5V,� SSTL_2)�

�W3�

�Y3�

�SDOCLK�

�SDICLK�

�O�

�I�

�DDR� Clock� Out� for� loopback� from� De-skew� PLL�

�DDR� Clock� In� from� loopback� to� De-skew� PLL.� This� pin� must� connect� to�

�SDOCLK� with� appropriate� de-skew� length.� See� Engineering� Evaluation� Design�

�Kit� for� detailed� implementation.�

�Y17,� Y16�

�W17,� W16�

�DDCLKO[3:2]�

�DDCLKON[3:2]�

�O�

�O�

�Factory� Reserved.�

�Factory� Reserved.�

�NAND/SRAM/ROM/EXIO� Interface�

�L2,� K1,� K2,�

�J3,� H5,� H4,�

�J2,� H3,� J1,�

�H2,� G5,� H1,�

�G3,� G4,� G2,�

�SADDR[23..0]�

�O�

�SRAM� Address� Bus.�

�The� 24-bit� address� bus� covers� 16M� word� memory� space� of�

�ROM/SRAM/FLASH,� and� 16M� byte� external� I/O� banks.�

�This� address� bus� is� shared� between� ROM/SRAM/FLASH/EXTIO� devices.�

�F1,� G1,� F2,�

�F3,� F5,� F4,�

�E1,� E2,� E3�

�May� 2011�

�10�

�M9999-051111-4.0�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

L17-RR-D1-F-01-100

CONN SOCKET 20-24AWG CRIMP GOLD

L171370

D-SUB BACKSHELL BLACK PLAS 9POS

L17529

D-SUB ASSY SPRING LATCH

L17D204182TX

SCREWLOCK W/NUT/WASH 1=10 SETS

L17D204182X

CONN ACCESSORY SCREW LOCK ASSY

L17D20419EX

D-SUB ASSY SCREW LOCK ASSY 10PCS

L17D20419X

CONN D-SUB ACCESSORY SCREW LOCK

L17D4K63110

D-SUB 9POS FEMALE DUST COVER

相关代理商/技术参数

KSZ9692PBI

功能描述:网络控制器与处理器 IC Integrated Gigabit Ethernet and Communication Controller with IPSec (I-temp)

RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

KSZ9692PB-PTP-EVAL

制造商:Micrel Inc 功能描述:Eval Board for KSZ9692 Integrated Gigabit Networking /Communications Controller

KSZ9692XPB

功能描述:网络控制器与处理器 IC Integrated gigabit Ethernet and USB Controller, Lead Free

RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

KT 10

制造商:Icotek 功能描述:Bulk

KT 1009

制造商:knitter-switch 功能描述:

KT 11

制造商:Icotek 功能描述:Bulk

KT 1117

制造商:knitter-switch 功能描述:

KT 12

制造商:Icotek 功能描述:Bulk 制造商:Weidmuller 功能描述:Bulk